для чего нужен регистр таблицы локальных дескрипторов

Внутренние регистры: Системные регистры

Системные регистры GDTR, LDTR и IDTR введены в процессорах начиная с Intel286 и предназначены для хранения базовых адресов таблиц дескрипторов — важнейших составляющих системной архитектуры при работе в защищенном режиме. Регистр задачи TR используется для слежения за тем, какая задача выполняется процессором в текущий момент.

Для доступа к системным регистрам используются команды: LGDT, SGDT, LLDT, SLDT, LIDT, SIDT, LTR, STR.

Регистр глобальной таблицы дескрипторов GDTR

Регистр глобальной таблицы дескрипторов GDTR содержит 32-битный (24-битный для Intel286) базовый адрес и 16-битный предел глобальной таблицы дескрипторов (GDT). Формат регистра GDTR приведен на рис. 1.4.

Рис. 1.4. Формат регистра глобальной таблицы дескрипторов

Регистр локальной таблицы дескрипторов LDTR

Видимая часть регистра локальной таблицы дескрипторов LDTR содержит только селектор дескриптора локальной таблицы дескрипторов (LDT). Сам дескриптор LDT автоматически загружается в скрытую часть LDTR из глобальной таблицы дескрипторов. Формат регистра LDTR приведен на рис. 1.5.

Рис. 1.5. Формат регистра локальной таблицы дескрипторов

Регистр таблицы дескрипторов прерываний IDTR

Регистр таблицы дескрипторов прерываний IDTR содержит 32-битный (24-битный для Intel286) базовый адрес и 16-битный предел таблицы дескрипторов прерываний (IDT). В реальном режиме может быть использован для изменения местоположения таблицы векторов прерываний. Формат регистра IDTR приведен на рис. 1.6.

Рис. 1.6. Формат регистра таблицы дескрипторов прерываний

Регистр задачи TR

Видимая часть регистра задачи TR содержит селектор дескриптора сегмента состояния задачи (TSS). Сам дескриптор TSS автоматически загружается в скрытую часть TR из глобальной таблицы дескрипторов. Формат регистра задачи приведен на рис. 1.7.

Рис. 1.7. Формат регистра задачи

Локальные дескрипторные таблицы

Выше было показано, что процессор i486 поддерживает три типа дескрипторных таблиц: общесистемные таблицы GDT и IDT, a также таблицы LDT. Последние таблицы при необходимости создаются по одной для каждой задачи и служат расщирением таблицы GDT при реализации мультизадачных систем. Наличие таблицы LDT увеличивает адресное пространство задачи, которое недоступно для других задач. Если задача не имеет таблицы LDT,что вполне допустимо, все требующиеся ей дескрипторы берутся из таблицы GDT; при этом необходимо избегать загрузки в сегментные регистры селекторов с битом TI = 1. Таким образом, с помощью таблиц LDT можно разрешить доступ к критическим областям памяти, например видеобуферу или дисковому контроллеру, только отдельным задачам.

Базовая структура адресного пространства с таблицами GDT и LDT предполагает, что каждая задача имеет свою таблицу LDT и все задачи пользуются общей таблицей GDT. В результате сегмент доступен либо только одной задаче, либо всем задачам. Для небольших однопользовательских систем характерно отсутствие таблиц LDT. Наконец, группа взаимосвязанных задач (образующих задание) может использовать одну и ту же таблицу LDT. Все задачи в группе разделяют одно адресное пространство, но группа, как целое, обладает своими сегментами, изолированными от остальной части системы. Более сложные структуры разделения адресного пространства реализуются с помощью альтернативного именования сегментов.

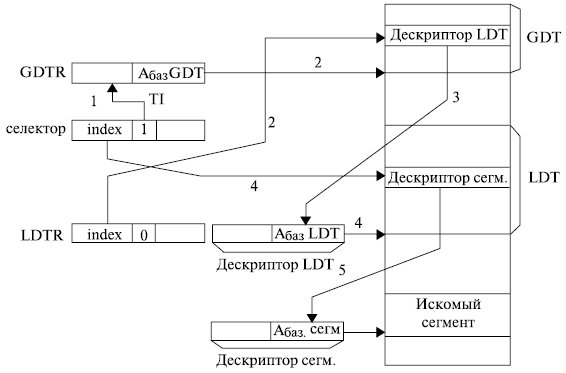

Локальная дескрипторная таблица, так же как таблица GDT, представляет собой массив 8-байтных дескрипторов сегментов. В любой момент времени процессор работает только с одной таблицей LDT, а при переключении задачи изменяется и активная таблица LDT. Поэтому для локализации таблицы LDT вместо 48-битного регистра, аналогичного регистрам GDTR и IDTR, в процессоре i486 имеется 16-битный регистр LDTR, содержащий только селектор LDT. Этот селектор выбирает в таблице GDT специальный дескриптор, который описывает текущую таблицу LDT, т.е. определяет ее базовый адрес и предел. Таким образом, при обращении к сегменту данных, который определяется селектором с битом TI = 1, появляется дополнительный уровень косвенности. Отметим, что в таблице LDT не могут находиться дескрипторы LDT, т.е. процессор не допускает дальнейшего «вложения косвенности».

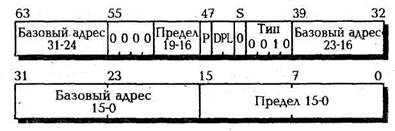

Дескриптор LDT, формат которого показан на рис.2.10, является первым примером системных дескрипторов сегментов с битом S = 0. Такие дескрипторы не имеют бита обращения А и за счет этого поле типа расширено до четырех бит. Для дескриптора LDT поле типа содержит 2 (0010В). В поле базового адреса находится базовый адрес таблицы LDT, а в поле предела — предел сегмента таблицы LDT. Для задания предела можно использовать все 20 бит; функционирует также бит гранулярности G, поэтому можно создать таблицу LDT с размером больше 64 Кбайт, но на практике этого не требуется.

| также не присутствуют. Процессор даже не разрешает загрузить регистр LDTR селектор неприсутствующей таблицы LDT. |

Отметим, что дескриптор LDT, как и любой другой дескриптор сегмента, имеет бит присутствия Р. Если дескриптор LDT отмечен неприсутствующим (Р = 0), считается, что все дескрипторы из LDT

|

Рис.2.10. Формат дескриптора таблицы LDT

Чтобы начать пользоваться таблицей LDT, нужно просто поместить в регистр LDTR селектор нужной таблицы. В этом отношении регистр LDTR действует как и любой другой сегментный регистр. Для сокращения числа обращений к памяти у регистра LDTR предусмотрен теневой регистр (он показан пунктиром на рис. 2.6), в который процессор автоматически считывает дескриптор LDT при загрузке селектора в регистр LDTR.

При попытке загрузить в регистр LDTR что-то отличающееся от селектора, выбирающего дескриптор LDT, процессор формирует общее нарушение защиты и «виноватый» селектор включается в стек как код ошибки. Когда в дескрипторе бит Р = 0, генерируется особый случай неприсутствия, а селектор по-прежнему будет служить кодом ошибки. Загрузка в регистр LDTR пустого селектора (значения 0000Н — 0003Н) допускается; такая операция сообщает процессору о том, что задача не будет пользоваться локальной дескрипторной таблицей.

Мы пока не касаемся дескрипторной таблицы прерываний IDT. Связано это с тем, что программам никогда не разрешается прямое обращение к IDT. Именно поэтому в селекторе достаточно одного бита индикатора таблицы TI. Таблицу IDT процессор i486 использует автоматически при обработке аппаратных и программных прерываний, которым посвящена следующая лекция.

2.1.7. Особенности сегментации

Процессор i486 разрешает создание сегментов, в которых допускаются операции только считывания, только исполнения, считывания/записи и исполнения/считывания. Однако в нем невозможно прямо создать характерные для процессора 8086 сегменты, в которых одновременно разрешены операции считывания, записи и исполнения. Тем не менее, образовать такие сегменты можно другими средствами.

Рис.2.11. Неперекрывающиеся сегменты памяти

В способе сегментации памяти процессора 8086 нет никаких трудностей для обращения по одному и тому же физическому адресу с привлечением различных сегментных регистров. Если, например, в регистрах DS и ES содержатся одинаковые начальные адреса, то оба регистра определяют один и тот же сегмент. Кроме того, как отмечалось выше, множество пар сегмент:смещение могут определять один и тот же физический адрес. Аналогичную ситуацию в процессоре i486 можно смоделировать путем тщательного подбора дескрипторов сегментов.

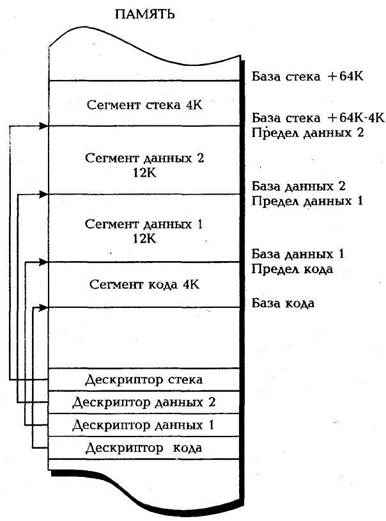

Обычно дескрипторы сегментов создаются во время инициализации системы для определения всех используемых областей памяти с учетом их назначения. Например, можно определить один сегмент кода для хранения машинных команд (т.е. собственно программы), один или два сегмента для данных и один сегмент для стека, рассчитанный на максимальный размер стекового кадра. Обычно эти сегменты должны занимать различные области памяти. При желании сегментам можно назначить соседние адреса так, чтобы конец одного сегмента совпадал с началом другого. На рис. 2.11 показаны неперекрывающиеся (непересекающиеся) сег мент кода 6 Кбайт, два сегмента данных по 12 Кбайт и сегмент стека 4 Кбайт.

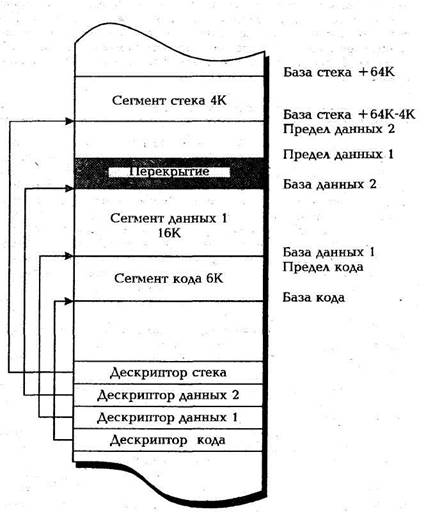

Представим теперь, что дескриптор первого сегмента данных изменен с целью увеличения его предела на 4 Кбайт. В этом случае два сегмента данных оказываются перекрывающимися, что показано на рис. 2.12. Такое перекрытие вполне допустимо, так как процессор i486 не накладывает никаких ограничений на определения перекрывающихся сегментов.

Перекрытие двух или более сегментов в некоторых отношениях может оказаться благоприятным. К любой ячейке в области перекрытия можно обращаться несколькими способами. Например, считывание по смещению 0 из сегмента данных 2 эквивалентно считыванию по смещению 3000Н из сегмента данных 1.

Выше говорилось, что процессор запрещает запись в сегменты, которые определены как исполняемые. Но не будет ошибкой запись в сегмент, который определен с разрешенной операцией записи и просто перекрывает то же линейное адресное пространство, что и исполняемый сегмент. Если дескрипторы сегмента кода и сегмента данных имеют одинаковые базовые адреса и пределы, то можно будет «модифицировать код» и «выполнять данные». Такой прием создания нескольких дескрипторов одного и того же адресного пространства называется альтернативным именованием (aliasing). Очевидно, дескрипторы можно считать именами сегментов; тогда несколько дескрипторов одного и того же сегмента (т.е. альтернативные имена) естественно назвать псевдонимами.

В предельной ситуации можно определить сегмент данных с разрешенными операциями записи и считывания, который имеет базовый адрес 0 и предел OFFFFFFFFH. Загрузка селектора такого дескриптора в сегментный регистр позволяет считывать и записывать по любому адресу всего линейного адресного пространства процессора i486. По существу, для любого сегмента в системе имеется альтернативное имя. Конечно, система не обязательно должна иметь физическую память 4 Гбайт; этот пример только показывает,

о попускается описывать несуществующее пространство памяти к же легко, как и перекрывающиеся диапазоны адресов.

Рис.2.12. Перекрывающиеся сегменты памяти

Перекрытие и альтернативное именование оказываются очень удобными для разделения данных между задачами. Например, создание для сегмента кода псевдонима в виде сегмента данных позволяет разработать самомодифицирующиеся программы. Упомянем еще один очень важный момент. Пространство, занятое дескрипторной таблицей, невозможно адресовать, не имея определяющего его дескриптора. Если не создать псевдонимов для дескрипторных таблиц в виде сегментов данных до перевода процессора i486 в Р-режим, то к таблицам будет невозможно обратиться. Конечно, определения этих сегментов должны быть максимально защищенными, так как разрешение всем программам доступа к таблицам GDT, IDT и LDT для считывания и записи приведет к катастрофическим последствиям.

Дата добавления: 2015-06-05 ; просмотров: 1665 ; ЗАКАЗАТЬ НАПИСАНИЕ РАБОТЫ

Лекция 3: Физическая и логическая организация адресного пространства

Сегментная организация памяти в защищенном режиме

Локальная таблица дескрипторов LDT используется для хранения дескрипторов, доступных только данной задаче. Их количество определяется количеством активных задач в системе.

Обращение разрешается, если уровень привилегий запроса не ниже, чем уровень привилегий дескриптора.

Он более сложен по сравнению с получением дескриптора из глобальной таблицы дескрипторов и проходит следующие этапы:

Поле адреса дескриптора, полученного из локальной или глобальной таблицы дескрипторов, определяет начало искомого сегмента. При суммировании полученного базового адреса сегмента и смещения в сегменте получается линейный адрес искомой ячейки памяти.

В случае если режим страничной адресации выключен (в регистре CR0 бит PG = 0), полученный линейный адрес равен физическому адресу искомого операнда или команды.

Рассмотрим подробнее процесс получения адреса операнда на примере команды

Формирование физического адреса операнда включает следующие действия (для сегментированного ЛАП):

Так как программа обычно редко модифицирует регистры с селекторами, в защищенном режиме она будет выполняться примерно с такой же скоростью, как и в реальном режиме.

Пишем свою ОС: Выпуск 2

Здравствуйте. Это снова мы, iley и pehat, с долгожданной второй статьёй из цикла «Пишем свою ОС» (первая статья здесь). Извиняемся за большую паузу после первой статьи, нам понадобилось некоторое время, чтобы определить дальнейшее направление нашей работы. В этом выпуске мы кратко рассмотрим защищённый режим 32-битных процессоров Intel. Ещё раз подчеркнём, что мы не ставим себе целью дать исчерпывающие теоретические данные.

Давайте на минуту вспомним нашу программу из предыдущего выпуска. Она запускалась вместо операционной системы и выводила сообщение «Hello world». Программа была написана на 16-битном ассемблере и работала в так называемом реальном режиме. Как вы наверняка знаете, при адресации в реальном режиме физический адрес формируется с помощью сегмента и смещения и имеет размерность 20 бит. Несложная математика подсказывает нам, что таким образом можно обращаться всего к мегабайту оперативной памяти.

Небольшой объём доступной памяти — это не единственная проблема реального режима. Представьте себе ситуацию, когда в памяти одновременно находится операционная система и несколько прикладных программ. В реальном режиме ничто не мешает любой из прикладных программ обратиться по адресу, принадлежащему другой программе или даже операционной системе. Таким образом, ошибка в одной программе может привести к краху всей системы.

Чтобы решить эти две проблемы, Intel в своё время разработали новый, значительно более сложный способ адресации оперативной памяти. Точнее, Intel разработали даже несколько способов адресации, и все они известны под собирательным названием защищённый режим.

Итак, адресация в защищённом режиме может происходить в одном из трёх режимов (извините за тавтологию) — в сегментном, страничном и сегментно-страничном. В этом выпуске мы рассмотрим только сегментный режим.

В сегментном режиме в памяти выделяются, как ни странно, сегменты. Эти сегменты значительно отличаются от простых и знакомых нам сегментов реального режима. В данном случае сегмент — это непрерывная область памяти, которая характеризуется базой, лимитом (т.е. грубо говоря, размером) и некими дополнительными атрибутами. База — это, грубо говоря, физический адрес, с которого начинается сегмент (на самом деле, это не физический адрес, а так называемый линейный, но об этом позже). Важно заметить, что, в отличие от сегментов реального режима, наши сегменты могут иметь произвольный размер. База, размер и атрибуты каждого сегмента хранятся в дескрипторе. Дескрипторы хранятся в специальных таблицах, а для выбора конкретного дескриптора из таблицы используются селекторы. Не пугайтесь такой кучи новых страшных слов, мы сейчас всё разложим по полочкам.

Итак, при каждом обращении к памяти процессор берёт из регистра (например, CS), селектор, находит по нему нужный дескриптор в таблице, извлекает из дескриптора адрес начала сегмента, прибавляет к адресу начала смещение и получает линейный адрес (обратите внимание, что линейный адрес и физический адрес — это разные вещи, но на данном этапе можно полагать, что это одно и то же). Кроме того, процессор проверяет, не вышел ли полученный адрес за границу сегмента и допускают ли атрибуты сегмента доступ к нему в данный момент. Схема вычисления линейного адреса выглядит примерно так:

Итак, как мы уже говорили, в дескрипторе хранится база (base address), размер (segment limit) и всякие дополнительные атрибуты сегмента. Давайте взглянем на схему дескриптора.

Обратите внимание, что под базу выделено 32 бита, а под лимит всего 20. Как же так, — спросите вы — разве нельзя создать сегмент, размер которого будет больше мегабайта? Можно. Для этого используется несложный трюк. Если бит G установлен в единицу, то лимит считается не в байтах, а в блоках по 4 Кбайт. Надо заметить, что лимит содержит размер сегмента минус один в единицах гранулярности, т.е. если лимит равен 0, то сегмент имеет размер 1 байт или 4 Кбайт. Кроме того, как вы видите, дескриптор включает ещё несколько полей. Их подробное описание можно найти, например, здесь.

Как упоминалось, дескрипторы хранятся в специальных таблицах. Таблиц может быть несколько, но в любом случае в памяти обязана присутствовать GDT — глобальная таблица дескрипторов. Она одна на всю операционную систему. В свою очередь, у каждой задачи, то есть процесса может быть ноль, одна или несколько LDT — локальных таблиц дескрипторов. Адрес и размер GDT хранится в регистре GDTR, текущей LDT — в регистре LDTR. Пока нам LDT не понадобится. Кроме того, бывают еще IDT — таблицы дескрипторов прерываний, но их рассмотрение отложим до следующего выпуска.

Для выбора дескриптора из таблицы используется структура данных, называемая селектором. Вот как он выглядит:

Селектор содержит в себе бит, указывающий, в какой таблице искать дескриптор, локальной или глобальной (L/G) и собственно номер дескриптора (descriptor number). Кроме того, у селектора есть поле RPL, но оно нас пока не интересует.

Итак, давайте перейдём к делу!

;Загрузить в CS:EIP точку входа в защищенный режим

O32 jmp 00001000b : pm_entry

Теперь немного поясним код.

После загрузки адреса и лимита глобальной таблицы дескрипторов в регистр GDTR идет поголовный запрет на прерывания. Объясняется это тем, что все обработчики прерываний работают в реальном режиме, и в защищенном режиме начнутся проблемы с адресацией. Так что пока строго-настрого запрещаем прерывания.

Для запуска программы нужно проделать манипуляции, полностью совпадающие с описанными в первой статье. Там же вы найдете список литературы на случай, если захотите узнать о защищенном режиме подробнее.

Нам не хватило фантазии на что-нибудь, демонстрирующее реальные возможности защищенного режима, поэтому мы снова выводим “Hello, World!”, но уже пользуясь прямым доступом к видеопамяти. Чтобы сделать что-нибудь красивое, было бы удобно воспользоваться прерываниями. Тому, как использовать их в защищенном режиме, будет посвящена следующая статья нашего цикла. А вторая статья на этом заканчивается. Будем рады увидеть ваши отзывы и пожелания.

2. Адресация памяти в защищенном режиме.

2.1 Дескрипторы и таблицы дескрипторов.

2.2 Страничное управление памятью, виртуальная память.

2.1 Дескрипторы и таблицы дескрипторов.

Существует три типа дескрипторных таблиц – глобальная таблица дескрипторов (одна в системе); локальная таблица дескрипторов (своя для каждой задачи); таблица дескрипторов прерываний (см. главу 4). Каждый дескриптор (элемент) таблицы описывает свой сегмент памяти. Сегменты памяти не пересекаются! Размер таблиц находится в пределах 8 байт – 64 Кбайт, что соответствует числу элементов в таблице от 1 до 8192.

Адрес начала каждой из таблиц (указатель на начало таблицы) хранится в специальных (программно доступных) регистрах процессора. Указатели на таблицу глобальных дескрипторов ( GDTR ) и таблицу прерываний ( IDTR ) имеют размер 48 байт, 32 из которых указывают линейный адрес начала таблицы, а остальные 16 – ее размер (предел).

Глобальная таблица ( GDT ) содержит дескрипторы, доступные все задачам. Может содержать дескрипторы любых типов, кроме дескрипторов прерываний и ловушек (см. главу 4). Нулевой элемент этой таблицы процессором не используется.

Дескрипторные таблицы создаются и поддерживаются операционной системой.

Дескрипторы сегментов кода и данных имеют следующий формат:

Адрес сегмента – физический адрес начала сегмента (если нет страничного преобразования);

Байт доступа – содержит информацию о защите сегмента;

1 – в страницах (по 4 Кб), при использовании страничной адресации памяти;

Дескрипторы системных сегментов имеют следующий формат:

Системные сегменты предназначены для хранения локальных таблиц дескрипторов LDT и состояния задач TSS (Task State Segment) (см. главу 5). Их дескрипторы определяют базовый адрес, лимит сегмента (1-64 Кбайт), права доступа (чтение, чтение/запись, только исполнение кода или исполнение/чтение) и присутствие сегмента в физической памяти. В байте управления доступом у этих дескрипторов бит Р определяет действительность (Р=1) или недействительность (Р=0) содержимого сегмента. Поле уровня привилегий DPL используется только в дескрипторах сегментов состояния задач ( TSS ). Поскольку обращение к дескрипторам LDT возможно только по привилегированным командам, поле DPL для дескрипторов локальных таблиц не используется. Поле Т YPE (1-3, 9-В) определяет тип сегмента:

· B — занятый сегмент состояния задачи 386+ (Busy TSS-386).

Дескрипторы шлюзов имеют следующий формат:

В байте управления доступом у этих дескрипторов бит Р определяет действительность (Р=1) или недействительность (Р=0) содержимого сегмента. Поле DPL задает уровень привилегий. Поле TYPE определяет тип шлюза:

Слово «Смещение» задает смещение (адрес) точки входа в целевом сегменте.

При использовании шлюзов может возникнуть исключение #GP, которое означает, что селектор указывает на некорректный тип дескриптора. При попытке использования недействительного шлюза (Р=0) возникает исключение #NР. (Подробнее о шлюзах см. главу 4, и главу 5).

Сегментные регистры в защищенном режиме играют роль селекторов (индексов дескрипторов в дескрипторных таблицах).

Формат селектора следующий:

RPL – номер запрашиваемого уровня привилегий;

Рассмотрим пример обращения процессора к памяти в сегмент (данных), описанный в глобальной дескрипторной таблице ( GDT ) – т.е. бит “ TI ” в селекторе сегмента равен нулю.

Старшие 13 байт селектора являются смещением искомого дескриптора от начала дескрипторной таблицы. Младшие байты играют роль атрибутов (см. выше), и при адресации внутри таблицы интерпретируются как нули – за счет чего происходит адресация таблицы по полю “ i ” с точностью до восьмибайтного слова, или (что в данном случае одно и тоже) до дескриптора. Адрес сегмента, прочитанный из дескриптора, складывается с внутрисегментным смещением и при отсутствии страничного преобразования адреса (см. ниже) выставляется на адресную шину.

2.2 Страничное управление памятью,

виртуальная память.

Страничное управление ( Paging ) является средством организации виртуальной памяти с подкачкой страниц по запросу ( Demand — Paged Virtual Memory ). В отличие от сегментации, которая организует программы и данные в модули различного размера, страничная организация оперирует с памятью, как с набором страниц одинакового размера. В момент обращения страница может присутствовать в физической оперативной памяти, а может быть выгруженной на внешнюю (дисковую) память. При обращении к выгруженной странице памяти процессор вырабатывает исключение # PF — отказ страницы, а программный обработчик исключения (часть ОС) получит необходимую информацию для свопинга — «подкачки» отсутствующей страницы с диска. Страницы не имеют прямой связи с логической структурой данных или программ. В то время как селекторы можно рассматривать как логические имена модулей кодов и данных, страницы представляют части этих модулей. Учитывая обычное свойство локальности (близкого расположения требуемых ячеек памяти) кода и ссылок на данные, в оперативной памяти в каждый момент времени следует хранить только небольшие области сегментов, необходимые активным задачам. Эту возможность (а следовательно, и увеличение допустимого числа одновременно выполняемых задач при ограниченном объеме оперативной памяти) как раз и обеспечивает страничное управление памятью. В первых 32-разрядных процессорах (начиная с i 80386) размер страницы составлял 4 Кбайт. Начиная с Pentium , появилась возможность увеличения размера страницы до 4 Мбайт, одновременно с использованием страниц размером 4 Кбайт. В Р6 имеется возможность расширения физического адреса до 36 бит (64 Гбайт), при котором могут использоваться страницы размером 4 Кбайт и 2 Мбайт.

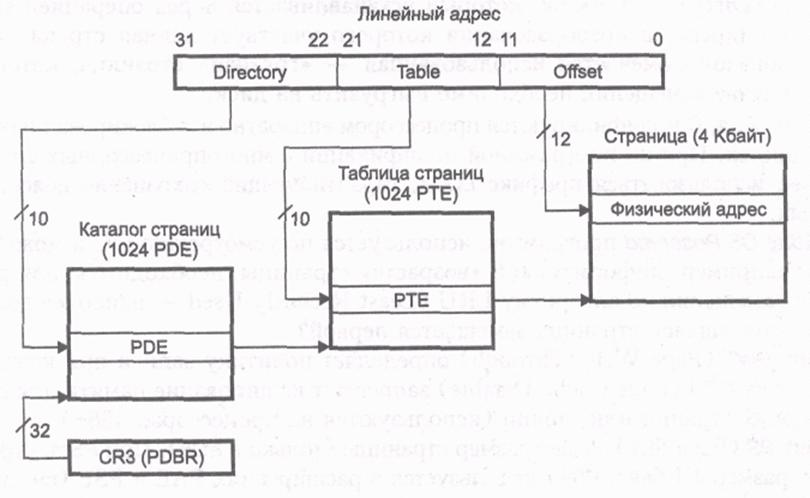

Базовый механизм страничного управления использует двухуровневую табличную трансляцию линейного адреса в физический.

Механизм имеет три части: каталог страниц ( Page Directory ), таблицы страниц ( Page Table ) и собственно страницы ( Page Frame ). Механизм включается установкой бита PG =1 в регистре CRO . Регистр CR 2 хранит линейный адрес отказа ( Page Fault Linear Address ) — адрес памяти, по которому был обнаружен последний отказ страницы. Регистр CR 3 хранит физический адрес каталога страниц ( Page Directory Physical Base Address ). Его младшие 12 бит всегда нулевые (каталог выравнивается по границе страницы).

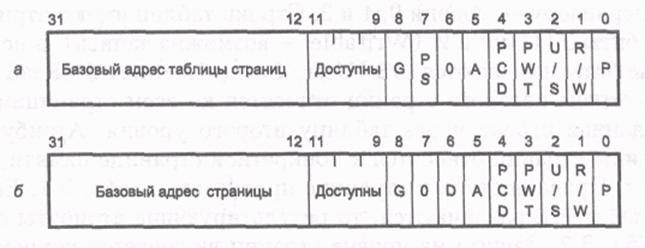

Каталог страниц, размером 4 Кбайт содержит 1024 32-битных строки Р D Е ( Page Directory Entry ). Каждая строка (см. ниже рис. а) содержит 20 старших бит адреса таблицы следующего уровня (младшие биты этого адреса всегда нулевые) и признаки (атрибуты) этой таблицы. Индексом поиска в каталоге страниц являются 10 старших бит линейного адреса (А22-А31).

а — строка каталога; б — строка таблицы

Каждая таблица страниц также имеет 1024 строки РТЕ ( Page Table Entry ) аналогичного формата (рис. б), но эти строки содержат базовый физический адрес ( Page Frame Address ) и атрибуты самих страниц. Индексом поиска в таблице являются биты А12-А21 линейного адреса. Физический адрес получается из адреса страницы, взятого из таблицы, и младших 12 бит линейного адреса. Строки каталога и таблиц имеют следующие биты атрибутов:

• A ( Accessed ) — признак доступа, который устанавливается перед любым чтением или записью по адресу, в преобразовании которого участвует данная строка.

• D ( Dirty ) — признак, который устанавливается перед операцией записи по адресу, в преобразовании которого участвует данная строка. Таким образом, помечается использованная — «грязная» страница, которую в случае замещения необходимо выгрузить на диск.

Поле OS Reserved программно используется по усмотрению ОС и может хранить, например, информацию о «возрасте» страницы, необходимую для реализации замещения по алгоритму LRU ( Least Recently Used — наиболее долго не использовавшаяся страница замещается первой).

Бит PWT ( Page Write Through ) определяет политику записи при кэшировании, а бит PCD ( Page Cache Disable ) запрещает кэширование памяти для обслуживаемых страниц или таблиц (используются на процессорах i 486+).

Бит PS ( Page Size ) задает размер страницы (только в РОЕ). При PS =0 страница имеет размер 4 Кбайт, PS =1 используется в расширениях РАЕ и PSE .

Бит G ( Global ), появившийся в Р6, определяет глобальность страницы. Он анализируется только в строке, указывающей на страницу физической памяти (в РТЕ для страниц в 4 Кбайт, в PDE — для страниц 2 Мбайт или 4 Мбайт). Этот бит, управляемый только программно, позволяет пометить страницы глобального использования (например, ядра ОС). При установленном бите PGE в регистре CR 4 строки с указателями на глобальные таблицы не будут аннулироваться в TLB при загрузке CR 3 или переключении задач, что снижает издержки обслуживания виртуальной памяти.